## High Accuracy, Full Protection & Diagnostics, Constant-Current RGB LED Driver with Sleep-Mode

#### 1. FEATURES

- 33 Constant-Current-Sink Output Channels

- 30-mA Maximum Output Current

- 5-V Maximum Output Voltage

- 3 Output Groups: OUTRn, OUTGn, OUTBn

- Output Current Adjustment

- 7-Bit Dot Correction for Each Channel

- 8-Bit Intensity Control for Each Group

- Integrated PWM Grayscale Generator

- PWM Dimming for Each Individual Channel

- Adjustable Global Grayscale Mode: 12-Bit, 10-Bit, 8-Bit

- Protection and Diagnostics

- LED-Open Detection, LED-Short Detection, Output Short-to-GND Detection

- Adjacent-Pin Short Detection

- Pre-Thermal Warning, Thermal Shutdown

- IREF Resistor Open- and Short-Detection and -Protection

- Negate Bit Toggle for GCLK Error Detect and LOD LSD Register Error Check

- LOS LSF Circuit Self-Test

- Programmable Output Slew Rate

- Output Channel Group Delay

- Support Serial Data Interface Communication from Simple 8-bit MCU

- Support Sleep Mode with supply current below 100uA

- High Accuracy: Typical +/-7% per channel

The HT1388 is designed for driving 33-channel LEDs Driver. It can supply a maximum 30mA constant output current set by an external resistor. The device has a 7-bit dot correction for each output. The device also has an 8-bit intensity control for the outputs of each color group.

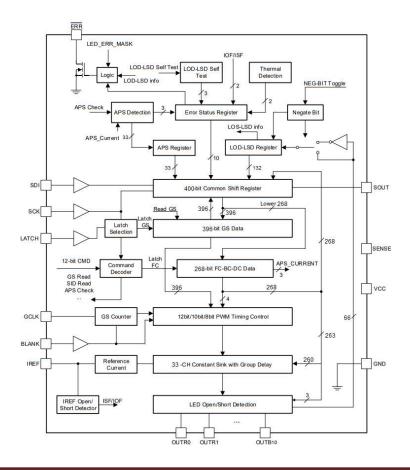

A 12-, 10-, or 8-bit grayscale control adjusts the intensity of each output. The device has circuits that sense faults in the system, including LED faults, adjacent-pin short faults, reference-resistor faults, and etc. Two slew rate control can be programmed for adjustment to get the largest decrease in system noise. There is an interval between the changes of output level from on LED group to a different one. This interval helps to decrease the starting electrical current. The SDI and SDO pins let more than one device be connected in series for control through one serial interface.

#### 4. PART NUMBER INFORMATION

| PART NO. | PACKAGE |

|----------|---------|

| HT1388FP | eQFP48  |

| HT1388FN | QFN48   |

#### 2. APPLICATIONS

- Automotive Interior & RGB Ambient Lighting

- Automotive Center Stack Display

- Automotive Shift-by-Wire and Gear Shifter

- Automotive Faceplate

- Automotive Local Dimming Display

#### 3. GENERAL DESCRIPTION

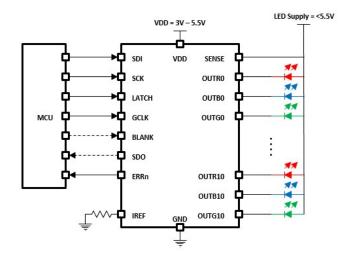

#### 5. TYPICAL APPLICATION

## 6. PIN CONFIGURATION AND DESCRIPTIONS

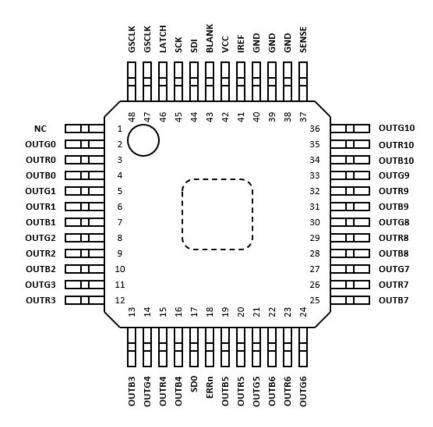

Pin assignment of HT1388FP

## **Pin Descriptions**

| Pin No.                        | Pin Name | 1/0 | Description                                                                                    |

|--------------------------------|----------|-----|------------------------------------------------------------------------------------------------|

| 44                             | SDI      | ı   | Serial data-in pin                                                                             |

| 45                             | SCK      | ı   | Data-shift clock-input pin                                                                     |

| 46                             | LATCH    | I   | Latch-enable input pin                                                                         |

| 47,48                          | GCLK     | I   | Clock input for grayscale PWM counter.<br>These two pins are connected together<br>internally. |

| 2,5,8,11,14,21,24,27,30,33,36  | OUTG0-10 | 0   | Constant-current outputs for color Green                                                       |

| 3,6,9,12,15,20,23,26,29,32,35, | OUTR0-10 | 0   | Constant-current outputs for color Red                                                         |

| 4,7,10,13,16,19,22,25,28,31,34 | OUTB0-10 | 0   | Constant-current outputs for color Blue                                                        |

# 芯高科技 HIGH TECH TECHNOLOGY LIMITED HT1388, 33-Channel, Internal-FET RGB LED Driver (Preliminary)

## **Pin Descriptions (continued)**

| Pin No.  | Pin Name    | 1/0 | Description                                                     |

|----------|-------------|-----|-----------------------------------------------------------------|

| 38,39,40 | GND         | -   | Power ground                                                    |

| 37       | SENSE       | I   | Connect to LED supply for LED diagnostics                       |

| 41       | IREF        | I   | Reference-current pin for setting the full-scale output current |

| 42       | VCC         | -   | Power supply pin                                                |

| 43       | BLANK       | I   | Blank all outputs. BLANK low for                                |

| 18       | ERRn        | 0   | Open-drain error feedback                                       |

| 17       | SDO         | 0   | Serial data-out pin                                             |

| 1        | NC          | -   | Not connected                                                   |

| -        | Thermal pad | -   | Connect to ground to improve thermal performance                |

11/2021 ver.1 **Private & Confidential** 3

## 7. SPECIFICATIONS

## 7.1. Absolute Maximum Ratings

|                                                 | PIN Name                     | Symbol            | Value                         | Unit  |

|-------------------------------------------------|------------------------------|-------------------|-------------------------------|-------|

|                                                 | Vcc                          |                   | -0.3 to 6                     | V     |

| Input Voltage                                   | SENSE                        |                   | -0.3 to 6                     | ٧     |

|                                                 | BLANK, GCLK, LATCH, SCK, SDI |                   | -0.3 to V <sub>CC</sub> + 0.3 | V     |

| Outrout Maltagra                                | ERRn, IREF, SDO              |                   | -0.3 to V <sub>CC</sub> + 0.3 | V     |

| Output Voltage                                  | OUTR0-10, OUTG0-10, OUTB0-10 |                   | -0.3 to 6                     | ٧     |

| Output Current                                  | OUTR0-10, OUTG0-10, OUTB0-10 |                   | 0 to 30                       | mA    |

| Junction temperature r                          | range                        | TJ                | -40 to +140                   | °C    |

| Maximum soldering temperature (at leads, 10sec) |                              | T <sub>LEAD</sub> | +300                          | °C    |

| Storage temperature range                       |                              | Ts                | -55 to +150                   | ۰C    |

| Junction to case(botto                          | m) thermal resistance        | θις               | 30                            | °C /W |

Remarks: 1) All voltages are with respect to GND unless otherwise noted.

## 7.2. ESD Ratings

|                            |                                                    | VALUE | Unit |  |  |

|----------------------------|----------------------------------------------------|-------|------|--|--|

| HT1388FN (QFN4             | HT1388FN (QFN48 package)                           |       |      |  |  |

| Electrostatic<br>Discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 | ±2000 | V    |  |  |

7.3. Recommended Operating Conditions

|                    |                                         | MIN     | NOM | MAX     | Unit |

|--------------------|-----------------------------------------|---------|-----|---------|------|

| V <sub>cc</sub>    | Supply input voltage                    | 3       |     | 5.5     | V    |

| V <sub>SENSE</sub> | LED supply voltage                      |         |     | 5.5     | V    |

| Vo                 | Output voltage                          |         |     | 5.5     | V    |

| V <sub>IL</sub>    | Input logic-low voltage                 | 0       |     | 0.3*Vcc | V    |

| V <sub>IH</sub>    | Input logic-high voltage                | 0.7*Vcc |     | Vcc     | V    |

| I <sub>OH</sub>    | High-level output source current at SDO |         |     | 1       | mA   |

|                    | Low-level output sink current at SDO    |         |     | 1       | mA   |

| l <sub>OL</sub>    | Low-level output sink current at ERRn   |         |     | 5       | mA   |

| lo                 | Constant output sink current            | 2       |     | 30      | mA   |

| T <sub>A</sub>     | Operating ambient temperature           | -40     |     | 125     | ∘C   |

| TJ                 | Operating junction temperature          | -40     |     | 150     | °C   |

11/2021 ver.1 Private & Confidential 5

## 7.4. Electrical Characteristics

Vcc = 5V, T<sub>J</sub>=25°C, V<sub>SENSE</sub> = 5V, GS=FFFh, BC=FFh, DC=7Fh with high DC RANGE (unless otherwise noted)

|                       | PARAMETER                           | TEST CONDITIONS                                                                                     | MIN                  | TYP   | MAX          | UNIT  |

|-----------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------|-------|--------------|-------|

| POWER                 | SUPPLIES                            |                                                                                                     | •                    |       |              | •     |

| Icc                   | Supply Current                      | SDI, SCK, LATCH=L, BLANK=L, GCLK=L, V <sub>OUT</sub> =1V, I <sub>OUT</sub> =2mA                     |                      | 6     |              |       |

|                       |                                     | SDI, SCK, LATCH=L, BLANK=L, GCLK=L, Vout=1V, Iout=20mA                                              |                      | 9     |              |       |

|                       |                                     | SDI, SCK, LATCH=L, BLANK=H, GCLK=8Mhz, V <sub>OUT</sub> =1V, I <sub>OUT</sub> =20mA, auto-repeat on |                      | 10    |              | mA    |

|                       |                                     | SDI, SCK, LATCH=L, BLANK=H, GCLK=8Mhz, V <sub>OUT</sub> =1V, I <sub>OUT</sub> =30mA, auto-repeat on |                      | 16    |              |       |

| Ishutdown             | Shutdown Current                    |                                                                                                     |                      |       | 100          | uA    |

| LOGIC IN              | PUTS (SDI, SCK, LATCH, C            |                                                                                                     |                      |       |              |       |

| $II_{kg}$             | Input leakage current               | At SDI, SCK, LATCH, with V <sub>I</sub> =V <sub>DD</sub> ;                                          |                      | 1     |              | uA    |

| $R_{pd}$              | Pull down resistance at BLANK, GCLK |                                                                                                     |                      | 500   |              | kΩ    |

| CONTRO                | L OUTPUTS (IREF, ERRn, )            |                                                                                                     |                      |       |              |       |

| VIREF                 | IREF voltage                        | R <sub>IREF</sub> =1600Ω                                                                            |                      | 1.220 |              | V     |

| Vон                   | High-level output voltage           | At SDO, I <sub>OH</sub> = -1mA                                                                      | V <sub>DD</sub> -0.4 |       |              | V     |

| $V_{OL}$              | Low-level output voltage            | At SDO, I <sub>OL</sub> = 1mA                                                                       |                      |       | 0.4          | V     |

| $V_{ERRn}$            | ERRn pin open-drain voltage drop    | I <sub>ERRn</sub> = 4mA                                                                             |                      |       | $0.1*V_{DD}$ | V     |

| I <sub>LKG_ERR</sub>  | ERRn pin leakage current            | V <sub>ERRn</sub> = 5V                                                                              |                      | 1     |              | uA    |

| OUTPUT                | STAGE                               |                                                                                                     |                      |       |              |       |

| $V_{(OUT,min)}$       | Minimum output voltage              | Vcc = 3V, I <sub>OUT</sub> = 30mA                                                                   |                      |       | 0.7          | V     |

| K <sub>(OUT)</sub>    | Current Gain                        | I <sub>ОUТ</sub> = 30mA                                                                             |                      | 40    |              | mA/mA |

| I <sub>LKG(OUT)</sub> | Output leakage current              | BLANK=L, Vout=5V                                                                                    |                      |       | 0.1          | uA    |

| CHANNE                | L ACCURACY                          |                                                                                                     |                      |       |              |       |

|                       |                                     | Vout=1V, RIREF = 24 k $\Omega$                                                                      |                      | 1.8   |              |       |

| $I_{(OUT)}$           | Constant output current             | Vout=1V, Riref = 1.6 k $\Omega$                                                                     |                      | 30    |              | mA    |

|                       |                                     | Vout=1V, RIREF open/ short                                                                          |                      | 10    |              |       |

## **Electrical Characteristics (continued)**

Vcc = 5V, T<sub>J</sub>=25°C, V<sub>SENSE</sub> = 5V, GS=FFFh, BC=FFh, DC=7Fh with high DC\_RANGE (unless otherwise noted)

|                                | PARAMETER                                                 | TEST CONDITIONS                            |       | YP MAX          | UNIT |

|--------------------------------|-----------------------------------------------------------|--------------------------------------------|-------|-----------------|------|

| LOGIC INP                      | UTS (SDI, SCK, LATCH, G                                   | CLK, BLANK)                                |       |                 |      |

| $\Delta I_{(\text{Ch-Ch})}$    | Current accuracy<br>(channel-to-channel in<br>same group) | Vout = 1V, lout = 30mA                     | -5%   | 5%              |      |

| $\Delta I_{(\text{Dev-Dev})}$  | Current accuracy (device-to-device)                       | Vout = 1V, lout = 30mA                     | -5%   | 5%              |      |

| $\Delta I_{(\text{Ch-Ideal})}$ | Current accuracy<br>(channel-to-ideal<br>output)          | Vout = 1V, lout = 30mA                     | -5%   | 5%              |      |

| $\Delta I_{(\text{OUT-VDD})}$  | Line Regulation                                           | Vout = 1V, lout = 30mA<br>Vcc = 3V to 5.5V | -1%   | 1%              | %/V  |

| $\Delta I_{(OUT\text{-VOUT})}$ | Load Regulation                                           | Vcc = 3V, lout = 30mA<br>Vout = 1V to 3V   | -1%   | 1%              | %/V  |

| PROTECT                        | ION CIRCUITS                                              |                                            |       |                 |      |

| $V_{\text{LOD1}}$              | LED open-circuit detection low threshold                  | LOD_VOLTAGE = 0b                           |       | 0.3             | V    |

| $V_{LOD2}$                     | LED open-circuit detection high threshold                 | LOD_VOLTAGE = 1b                           |       | 0.5             | V    |

| V <sub>LSD1</sub>              | LED short-circuit detection low threshold                 | LSD_VOLTAGE = 0b                           | Vsens | SE - 0.3        | V    |

| V <sub>LSD2</sub>              | LED short-circuit detection high threshold                | LSD_VOLTAGE = 1b                           | Vsens | se <b>-</b> 0.7 | V    |

| IREF_OC                        | Riref open-circuit detection threshold                    | Vcc = 5V                                   |       | 10              | uA   |

| IREF_OC_HYS                    | Riref open-circuit detection hysteresis                   | Vcc = 5V                                   |       | 5               | uA   |

| IREF_SC                        | Riref short-circuit detection threshold                   | Vcc = 5V                                   | 2     | 2.4             | mA   |

| IREF_SC_HYS                    | Riref short-circuit detection hysteresis                  | Vcc = 5V                                   | (     | 0.3             | mA   |

| T <sub>PTW</sub>               | Pre-Thermal warning flag threshold                        | Junction temperature                       | 1     | 35              | °C   |

| T <sub>PTW_HYS</sub>           | Pre-Thermal warning flag hysteresis                       | Junction temperature                       |       | 10              | °C   |

| T <sub>TEF</sub>               | Thermal error flag threshold                              | Junction temperature                       | 1     | °C              |      |

| T <sub>TEF_HYS</sub>           | Thermal error flag hysteresis                             | Junction temperature                       |       | 10              | °C   |

## 7.5 Timing Requirements

$V_{CC} = 3 \text{ V to } 5.5 \text{ V, TJ} = -40^{\circ}\text{C to } 150^{\circ}\text{C}.$

|                  | 0 5.5 V, 1340 C to 150 C.                                                         | MIN               | NOM | MAX | UNIT |

|------------------|-----------------------------------------------------------------------------------|-------------------|-----|-----|------|

| fclk(sck)        | SCK data-shift clock frequency                                                    |                   |     | 4   | MHz  |

| fclk(gclk)       | GCLK grayscale clock frequency                                                    |                   |     | 8   | MHz  |

| t <sub>WH0</sub> | SCK high pulse duration                                                           | 60                |     |     | ns   |

| t <sub>WL0</sub> | SCK low pulse duration                                                            | 60                |     |     | ns   |

| t <sub>WH1</sub> | LATCH high pulse duration                                                         | 80                |     |     | ns   |

| t <sub>WL1</sub> | LATCH low pulse duration                                                          | 80                |     |     | ns   |

| t <sub>WL2</sub> | BLANK pulse duration                                                              | T <sub>GCLK</sub> |     |     | ns   |

| t <sub>WH3</sub> | GCLK high pulse duration                                                          | 40                |     |     | ns   |

| t <sub>WL3</sub> | GCLK low pulse duration                                                           | 40                |     |     | ns   |

| t <sub>SU0</sub> | SDI - SCK↑ setup time                                                             | 55                |     |     | ns   |

| t <sub>SU1</sub> | BLANK↑– GCLK↑ setup time                                                          | 60                |     |     | ns   |

| t <sub>SU2</sub> | LATCH↑ – SCK↑ setup time                                                          | 200               |     |     | ns   |

| t <sub>SU3</sub> | LATCH↑ for GS data – GCLK↑ when display timing reset mode is disabled, setup time | 90                |     |     | ns   |

| t <sub>SU4</sub> | LATCH↑ for GS data – GCLK↑ when display timing reset mode is enabled, setup time  | 150               |     |     | ns   |

| t <sub>H0</sub>  | SCK↑– SDI hold time                                                               | 55                |     |     | ns   |

| t <sub>H1</sub>  | SCK↑– LATCH↑ hold time                                                            | 85                |     |     | ns   |

| t <sub>H2</sub>  | SCK↑- LATCH↓ hold time                                                            | 55                |     |     | ns   |

| t <sub>RI0</sub> | SDI, SCK, LATCH rise time                                                         |                   |     | 50  | ns   |

| t <sub>RI1</sub> | GCLK rise time                                                                    |                   |     | 30  | ns   |

| t <sub>FI0</sub> | SDI, SCK, LATCH fall time                                                         |                   |     | 50  | ns   |

| t <sub>FI1</sub> | GCLK fall time                                                                    |                   |     | 30  | ns   |

## 7.6 Switching Characteristics

Over operating junction temperature range (unless otherwise noted)

|                  | PARAMETER                           | TEST CONDITIONS                                            | MIN | TYP        | MAX | UNIT |

|------------------|-------------------------------------|------------------------------------------------------------|-----|------------|-----|------|

| t <sub>ro0</sub> | Rise time from 10% Vspo to 90% Vspo |                                                            |     | 60         |     | ns   |

| t <sub>ro1</sub> | Rise time from 10% Vout to 90% Vout | IOUT = 30mA, SLEW_RATE = 0b<br>IOUT = 30mA, SLEW_RATE = 1b |     | 220<br>120 |     | ns   |

| t <sub>fo0</sub> | Fall time from 90% Vspo to 10% Vspo | _                                                          |     | 60         |     | ns   |

| t <sub>fo1</sub> | Fall time from 90% Vout to 10% Vout | IOUT = 30mA, SLEW_RATE = 0b<br>IOUT = 30mA, SLEW_RATE = 1b |     | 220<br>120 |     | ns   |

| t <sub>pd0</sub> | Propagation delay, SCK↑ to SDO      | _                                                          |     | 140        |     | ns   |

| t <sub>pd1</sub> | Propagation delay,<br>LATCH↑ to SDO |                                                            |     | 180        |     | ns   |

## **Switching Characteristics (continued)**

Over operating junction temperature range (unless otherwise noted)

|                   | PARAMETER                                                        | TEST CONDITIONS                        | MIN | TYP      | MAX | UNIT |

|-------------------|------------------------------------------------------------------|----------------------------------------|-----|----------|-----|------|

| t <sub>pd2</sub>  | Propagation delay, BLANK↓ to OUTR0, -G0, -B0, -R6, -G6, -B6 off  |                                        |     | 100      |     | ns   |

| t <sub>pd3</sub>  | Propagation delay, GCLK↑ to OUTR0, -G0, -B0, -R6, -G6, -B6 on    |                                        |     | 100      |     | ns   |

| t <sub>pd4</sub>  | Propagation delay, GCLK↑ to OUTR1, -G1, -B1, -R7, -G7, -B7 on    |                                        |     | 150      |     | ns   |

| t <sub>pd5</sub>  | Propagation delay, GCLK↑ to OUTR2, -G2, -B2, -R8, -G8, -B8 on    |                                        |     | 200      |     | ns   |

| t <sub>pd6</sub>  | Propagation delay, GCLK↑ to OUTR3, -G3, -B3, -R9, -G9, -B9 on    |                                        |     | 250      |     | ns   |

| t <sub>pd7</sub>  | Propagation delay, GCLK↑ to OUTR4, -G4, -B4, -R10, -G10, -B10 on |                                        |     | 300      |     | ns   |

| t <sub>pd8</sub>  | Propagation delay, GCLK↑ to OUTR5, -G5, -B5 on                   |                                        |     | 350      |     | ns   |

| t <sub>pd9</sub>  | Propagation delay, LATCH↑ to Vout                                |                                        |     | 80       |     | ns   |

| t <sub>pd10</sub> | Propagation delay, LATCH↑ to APS_FLAG change                     | APS_CURRENT = 0b<br>APS_CURRENT = 1b   |     | 10<br>20 | -   | us   |

| t <sub>pd11</sub> | Propagation delay, LATCH↑ to LOD_LSD_FLAG change                 | No failure in LOD_LSD detector circuit |     | 10       |     | us   |

11/2021 ver.1 Private & Confidential 9

## 8 Detailed Description

#### 8.1.1 Overview

In automotive indicator and local dimming backlighting applications, the demand for multi-channel constant-current LED drivers are increasing to achieve uniformity of LED brightness and color temperature. System-level safety considerations require fault-detection capability and device self-check features.

The HT1388 device is an automotive 33-channel constant-current RGB LED driver with LED diagnostics. The HT1388 device provides up to 30-mA output current set by an external resistor. The current can be adjusted by 7-bit dot correction with two subranges for individual output and an 8-bit brightness control for the outputs of each color group. The brightness can be adjusted individually for each channel through a 12-,10-, or 8-bit grayscale control. Fault-detection circuits are available to detect system faults including LED faults, adjacent-pin short faults, reference-resistor faults, and more. Negate bit toggle and LOD-LSD self-test provide a device self-check function to improve system reliability. Configurable slew-rate control optimizes the noise generation of the system and improves the system EMC performance. Output-channel group delay helps to reduce inrush current to optimize the system design. The SDI and SDO pins allow more than one device to be connected in a daisy chain for control through one serial interface.

### 8.1.2 Functional Block Diagram

#### 8.2 Feature Description

#### 8.2.1 Maximum Constant-Sink-Current Setting

LED full-scale current can be programmed using an external resistor connected between the IREF pin and GND. The R<sub>IREF</sub> resistor value is calculated with the following formula.

$$\begin{split} R_{IREF} = K \, \times \, \frac{V_{IREF}}{I_{(OUT)max}} \end{split} \label{eq:Rire}$$

where

- V<sub>IREF</sub> is the reference voltage

- · K is the IREF-current to output-current ratio

I<sub>(OUT)max</sub> is full-scale current for each output (1)

Figure 15 shows the reference resistor calculation curve.

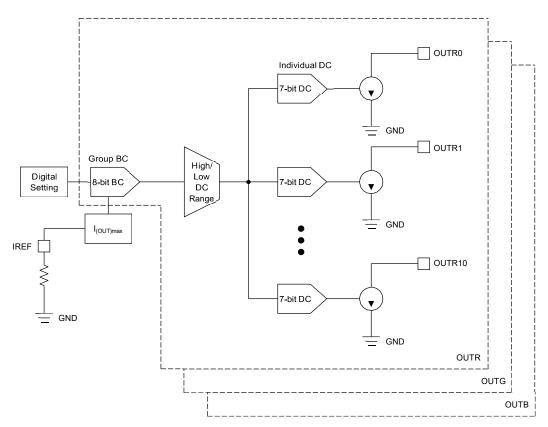

#### 8.2.2 Brightness Control and Dot Correction

The HT1388 device implements an 8-bit group brightness control (BC) and 7-bit individual dot correction (DC) to calibrate the output current. The 33 output channels are divided into three groups: OUTRn, OUTGn, and OUTBn. Each group contains 11 output channels. There are two configurable ranges for the DC value of each group. One is the low DC range with output current from 0 to 66.7%  $I_{(OUT)max}$ . The other is the high DC range with output current from 33.3%  $I_{(OUT)max}$  to 100%  $I_{(OUT)max}$ . The IREF resistor, BC, DC, and DC range together determine the channel output current, as shown in Figure 21. Equation 2 and Equation 3 are the detailed output current calculation formulas.

Equation 2 determines the output sink current for each color group when DC is in the high adjustment range.

$$I_{OUT} = \left(\frac{1}{3} \times I_{(OUT)max} + \frac{2}{3} \times I_{(OUT)max} \times \frac{DC}{127}\right) \times \frac{BC}{255}$$

(2)

Equation 3 determines the output sink current for each color group when DC is in the low adjustment range.

$$I_{OUT} = \frac{2}{3} \times I_{(OUT)max} \times \frac{DC}{127} \times \frac{BC}{255}$$

(3)

#### **Feature Description (continued)**

Figure 21. Brightness Control and Dot Correction Block Diagram

#### 8.2.3 Grayscale Configuration

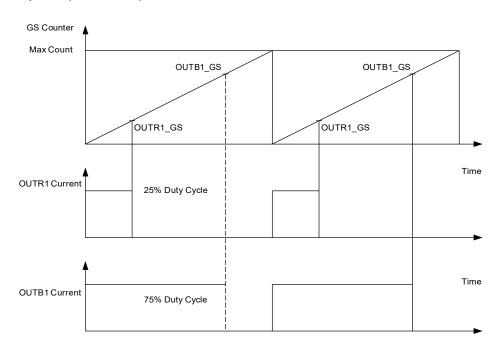

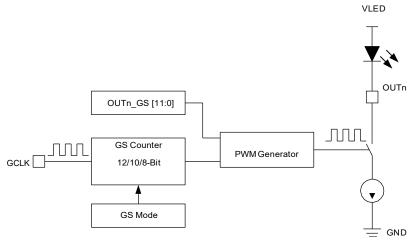

The HT1388 device implements a grayscale configuration function to realize the individual PWM dimming function for the output channels. The grayscale has three global configuration modes, 12-bit, 10-bit and 8-bit. The GCLK input provides the clock source for the internal PWM generator. The GS counter counts the GCLK number and compares the number with the channel grayscale register value. The output channel turns off when the GS counter value reaches the grayscale register value. Figure 22 shows the detailed block diagram of the PWM generator.

To restart a new PWM cycle, users can use two methods. One is to toggle the BLANK pin after the GS counter reaches the maximum count value, because BLANK low resets the GS counter and BLANK high restarts the GS counter. Another is to pull BLANK high and set the AUTO\_REPEAT&TIMING\_RESET register bit to 1. The PWM starts a new cycle automatically after the GS counter reaches the maximum count value.

## **Feature Description (continued)**

Time

12-bit GS mode, Max Count = 4096 10-bit GS mode, Max Count = 1024 8-bit GS mode, Max Count = 256

Figure 22. PWM Generator

11/2021 ver.1 Private & Confidential 13

#### 8.3.3.1 PWM Auto Repeat

The PWM auto repeat function is configured by the AUTO\_REPEAT bit. The AUTO\_REPEAT bit is 0 by default, and the PWM auto repeat function is disabled under this condition. The PWM cycle only executes once, so users must toggle BLANK to restart a new PWM cycle. Figure 11 and Figure 12 show the PWM operation in this mode. When the AUTO\_REPEAT bit is 1, the PWM auto repeat function is enabled. The PWM cycle automatically repeats as long as BLANK is high and GCLK is present, as shown in Figure 13.

#### **Feature Description (continued)**

### 8.3.3.2 PWM Timing Reset

PWM timing reset function is configured by the TIMING\_RESET bit. The PWM timing reset function can restart a PWM cycle with newly configured duty-cycle after a GS data write. The TIMING\_RESET bit is 0 by default, The PWM timing reset function is disabled in this condition. The PWM duty cycle is not influenced by a GS data write. The newly configured PWM duty-cycle only is valid after the current PWM cycle finishes. When the TIMING\_RESET bit is 1, the PWM timing reset function is enabled, and the PWM cycle restarts with the new PWM duty-cycle immediately after the GS data write.

#### 8.3.4 Diagnostics

The HT1388 device integrates a full LED diagnostics functionality, such as LED open detection (LOD), LED short detection (LSD), and output short-to-GND detection (OSD), which improves the system safety.

#### 8.3.4.1 LED Diagnostics

An LOD-LSD detection circuit compares the output voltage with the LOD threshold and LSD threshold, and the output results show in Table 1.

**Table 1. LOD-LSD Detection**

| CUITRUT VOLTAGE COMPITION                     | DETECTOR OUTPUT BIT VALUE |     |  |  |  |

|-----------------------------------------------|---------------------------|-----|--|--|--|

| OUTPUT VOLTAGE CONDITION                      | LOD                       | LSD |  |  |  |

| V <sub>OUTn</sub> < LOD_VOLTAGE               | 1                         | 0   |  |  |  |

| LOD_VOLTAGE < V <sub>OUTn</sub> < LSD_VOLTAGE | 0                         | 0   |  |  |  |

| V <sub>OUTn</sub> > LSD_VOLTAGE               | 0                         | 1   |  |  |  |

The LOD threshold can be configured by the LOD\_VOLTAGE bit. The threshold is 0.3 V when LOD\_VOLTAGE = 0, and the threshold is 0.5 V when LOD\_VOLTAGE = 1.

Table 2. LOD Threshold

| LOD_VOLTAGE BIT | LOD THRESHOLD |

|-----------------|---------------|

| 0 (Default)     | 0.3 V         |

| 1               | 0.5 V         |

LSD threshold is configured by the LSD\_VOLTAGE bit. The threshold is  $V_{VSENSE} - 0.3 \text{ V}$  when LSD\_VOLTAGE = 0, and the threshold is VSENSE - 0.7 V when LSD\_VOLTAGE = 1.

Table 3. LSD Threshold

| LSD_VOLTAGE BIT | LSD THRESHOLD              |

|-----------------|----------------------------|

| 0 (Default)     | V <sub>SENSE</sub> – 0.3 V |

| 1               | V <sub>SENSE</sub> – 0.7 V |

There are two sets of LOD-LSD registers in the device. One is the LOD1-LSD1 registers, another is the LOD2-LSD2 registers. Each group of registers consists of 33 bits of LOD data and 33 bits of LSD data, corresponding to 33 channel outputs. The device updates the LOD1-LSD1 registers at the 9th GCLK rising edge. The device updates the LOD2-LSD2 registers the Nth GCLK rising edge. N is the maximum GCLK number in a PWM period minus 1, see Table 4.

To detect all kinds of LED faults, the output channel should turn ON at the 9th GCLK rising edge, and turn OFF at the Nth GCLK rising edge.

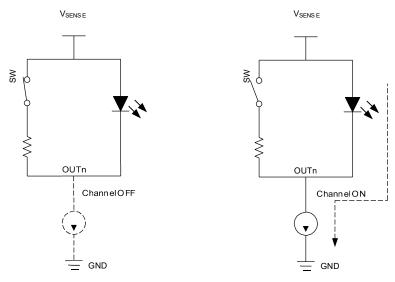

The device integrates an internal pullup circuit for LED diagnostics, shown in Figure 23. The circuit turns off during the channel on-state, but turns on to charge the output pin during the channel off-state. For an LED-short fault, both LSD1 and LSD2 are 1. For an LED-open fault, both LOD1 and LSD2 are 1. For an output short-to-GND fault, both LOD1 and LOD2 are 1. Table 5 shows the details.

11/2021 ver.1 Private & Confidential 15

Figure 23. Internal Pullup Circuit

**Table 4. LOD-LSD Register Latch Timing**

| GS COUNTER MODE | LOD1-LSD1            | LOD2-LSD2               |

|-----------------|----------------------|-------------------------|

| 12-bit          | 9th GCLK rising edge | 4095th GCLK rising edge |

| 10-bit          | 9th GCLK rising edge | 1023rd GCLK rising edge |

| 8-bit           | 9th GCLK rising edge | 255th GCLK rising edge  |

**Table 5. LED Status Lookup Table**

|                     |                                           |   | •              |                                                          |  |

|---------------------|-------------------------------------------|---|----------------|----------------------------------------------------------|--|

| I ED OTATUO         | LOD-LSD RESULT                            |   |                |                                                          |  |

| LED STATUS          | LOD1-LSD1 UPDATED AT 9 <sup>th</sup> GCLK |   | LOD2-LSD2 UPDA | LOD2-LSD2 UPDATED AT N <sup>th</sup> GCLK <sup>(1)</sup> |  |

| LED Ok              | LOD1                                      | 0 | LOD2           | 0                                                        |  |

| LED OK              | LSD1                                      | 0 | LSD2           | 1                                                        |  |

| ED anan             | LOD1                                      | 1 | LOD2           | 0                                                        |  |

| LED open            | LSD1                                      | 0 | LSD2           | 1                                                        |  |

| ED abort            | LOD1                                      | 0 | LOD2           | 0                                                        |  |

| LED short           | LSD1                                      | 1 | LSD2           | 1                                                        |  |

| Output short-to-GND | LOD1                                      | 1 | LOD2           | 1                                                        |  |

|                     | LSD1                                      | 0 | LSD2           | 0                                                        |  |

<sup>(1)</sup> N = 4095 for 12-bit GS mode, 1023 for 10-bit GS mode, 255 for 8-bit GS mode

In some cases, users may need to turn off output channels before the 9th GCLK to disable output channels, or turn on output channels at Nth GCLK to get more brightness. LOD\_LSD faults are reported as shown in Table 6. Users can ignore the fault according to the GS register setting value.

**Table 6. PWM Status Lookup Table**

|                        | LOD-LSD RESULT                |   |                |                    |

|------------------------|-------------------------------|---|----------------|--------------------|

| PWM STATUS             | LOD1-LSD1 UPDATED AT 9th GCLK |   | LOD2-LSD2 UPDA | TED AT Nth GCLK(1) |

| DWW OK                 | LOD1                          | 0 | LOD2           | 0                  |

| PWM OK                 | LSD1                          | 0 | LSD2           | 1                  |

| Channel off before 9th | LOD1                          | 0 | LOD2           | 0                  |

| GCLK                   | LSD1                          | 1 | LSD2           | 1                  |

| Channel on at Nth GCLK | LOD1                          | 0 | LOD2           | 0                  |

|                        | LSD1                          | 0 | LSD2           | 0                  |

<sup>(1)</sup> N = 4095 for the 12-bit GS mode, 1023 for the 10-bit GS mode, 255 for the 8-bit GS mode

The LOD\_LSD status is updated every PWM cycle. Figure 14 is an example of the LOD-LSD register update timing for the 12-bit GS mode.

#### 8.3.4.2 Adjacent-Pin-Short Check

The device implements the APS check function to detect the adjacent-pin short failures during system initialization. TI recommends to do an APS check when channels are all off. The APS check can be executed by writing the APS check command.

If there is no adjacent-pin short failure, the device passes the APS check and 011b is latched into APS FLAG in the error status register. The 33-bit APS register is 0. If there are two adjacent pins shorted, 110b is latched into APS\_FLAG in the error status register. The corresponding bit in the APS register is set to 1. Users can read out the 33-bit data from the APS register to check which channel has the APS failure. Table 7 shows the details of the APS\_FLAG and APS register. Table 8 shows the bit arrangement of the APS register. To read this APS information, see Table 22.

Table 7. APS Flag and APS Register

|                                     | J     | •                                            |

|-------------------------------------|-------|----------------------------------------------|

| REGISTER                            | VALUE | DESCRIPTION                                  |

| ADC FLAC                            | 011b  | Pass, no adjacent pins short                 |

| APS_FLAG                            | 110b  | Fail, adjacent pins short                    |

| Dit is ADO society (00 Little to 1) | 0b    | This OUTn pin is not shorted with other pins |

| Bit in APS register (33-bit total)  | 1b    | This OUTn pin is shorted with other pins     |

Table 8. Bit Arrangement of the APS Register

| BIT OF APS REGISTERS | CORRESPONDING OUTPUTS |

|----------------------|-----------------------|

| Bit 32               | OUTB10                |

| Bit 31               | OUTB9                 |

| Bit 30               | OUTB8                 |

| Bit 29               | OUTB7                 |

| Bit 28               | OUTB6                 |

| Bit 27               | OUTB5                 |

| Bit 26               | OUTB4                 |

| Bit 25               | OUTB3                 |

| Bit 24               | OUTB2                 |

| Bit 23               | OUTB1                 |

| Bit 22               | OUTB0                 |

| Bit 21               | OUTG10                |

Table 8. Bit Arrangement of the APS Register (continued)

| BIT OF APS REGISTERS | CORRESPONDING OUTPUTS |

|----------------------|-----------------------|

| Bit 20               | OUTG9                 |

| Bit 19               | OUTG8                 |

| Bit 18               | OUTG7                 |

| Bit 17               | OUTG6                 |

| Bit 16               | OUTG5                 |

| Bit 15               | OUTG4                 |

| Bit 14               | OUTG3                 |

| Bit 13               | OUTG2                 |

| Bit 12               | OUTG1                 |

| Bit 11               | OUTG0                 |

| Bit 10               | OUTR10                |

| Bit 9                | OUTR9                 |

| Bit 8                | OUTR8                 |

| Bit 7                | OUTR7                 |

| Bit 6                | OUTR6                 |

| Bit 5                | OUTR5                 |

| Bit 4                | OUTR4                 |

| Bit 3                | OUTR3                 |

| Bit 2                | OUTR2                 |

| Bit 1                | OUTR1                 |

| Bit 0                | OUTR0                 |

APS\_FLAG and the APS registers are all 0 by default. After an APS check command, APS\_FLAG should be 011b or 110b. Otherwise there is a failure in the APS check circuit. If the APS check result fails, the ERRn pin is pulled low, the APS\_FLAG value is 110b, and the ERRn pin status stays unchanged until the fault is removed and the user executes an ERROR clear command. Figure 5 and Figure 9 show more detail.

As different LEDs have different parasitic capacitance, to make sure the APS Check function is suitable for all kinds of LEDs, the device provides two configuration bits for APS current and APS time. The APS current is selected by APS\_CURRENT as shown in Table 9. The APS time is selected by APS\_TIME as shown in Table 10.

**Table 9. APS Current Selection**

| APS_CURRENT BIT | APS CURRENT |

|-----------------|-------------|

| 0b              | 20 μΑ       |

| 1b              | 40 μΑ       |

#### **Table 10. APS Time Selection**

| APS_TIME BIT | ADJACENT-PIN-SHORT DETECTION TIME |

|--------------|-----------------------------------|

| 0b           | 10 µs                             |

| 1b           | 20 μs                             |

#### 8.3.4.3 IREF Short and IREF Open Detection

To protect the device from a reference-resistor short or open fault, the device integrates IREF short and open protection. In an IREF short or open fault condition, the device reports the fault and sets the output current to a default value to help improve the system safety.

By default, the ISF and IOF flags are 0. When the IREF current exceeds the fault-detection threshold, the ERRn pin is pulled down, the ISF or IOF flag is set to 1. The error flag and ERRn pin status stay unchanged until the fault is removed and there is an ERROR clear command.

Once there is an ISF or IOF failure, the output current is set to a default value,  $I_{(OUT)max}$ , of 10 mA, see Table 11. Once the ISF or IOF failure is removed, the output current returns back to the IREF setting value immediately.

| I <sub>IREF</sub>                  | ISF | IOF | OUTPUT                                         |

|------------------------------------|-----|-----|------------------------------------------------|

| I <sub>IREF</sub> ≤ 10 μA          | 0   | 1   | I <sub>(OUT)max</sub> = 10 mA                  |

| 10 μA < I <sub>IREF</sub> ≤ 2.3 mA | 0   | 0   | $I_{(OUT)max} = V_{IREF} \times 40 / R_{IREF}$ |

| IIDEE > 3 mA                       | 1   | 0   | I <sub>(OUT)</sub> = 10 mA                     |

Table 11. Criteria of ISF/IOF Judgement and Corresponding Actions

#### 8.3.4.4 Pre-Thermal Warning Flag

The HT1388 device implements a pre-thermal warning (PTW) function. Once the junction temperature exceeds the PTW threshold, the ERRn pin is pulled low, the PTW flag in error status register is set to 1, the PTW\_FLAG and ERRn pin status stay unchanged until the junction temperature drops below TPTW – THYS PTW, and there is an ERROR clear command.

#### 8.3.4.5 Thermal Error Flag

The HT1388 device monitors junction temperature all the time. Once the junction temperature exceeds the thermal shutdown threshold, all of the constant-current outputs turn off, the ERRn pin is pulled low, the thermal error flag and ERRn pin status are set to 1 and stay unchanged until the fault is removed and there is an ERROR clear command. During this state, all the digital functions work normally, and users can read or write data through common shift registers. After the junction temperature drops below  $T_{TEF} - T_{HYS\_TEF}$ , the device goes back to normal operation again. Users can reset the TEF flag by sending an ERROR clear command.

#### 8.3.4.6 Negate Bit Toggle

The HT1388 device implements a Negate Bit Toggle function to check the LOD-LSD registers, which is useful for safety-related applications.

There are NEG1 and NEG2 bits in the registers, and the values are both 0 by default. After executing the Negate Bit Toggle command, both NEG1 and NEG2 change to 1. The LOD-LSD results are reversed under this condition. If the LOD-LSD registers get stuck, the LOD-LSD results are not reversed, which means there is a fault in the LOD-LSD registers.

The LOD1-LSD1 registers only update on the 9th GCLK rising edge, and the LOD2-LSD2 registers only update on the Nth GCLK rising edge. So, after the Negate Bit Toggle command, users must wait for at least one GS counter cycle (4096 GCLKs for the 12-bit GS counter mode, 1024 GCLKs for the 10-bit GS counter mode, or 256 GCLKs for the 8-bit GS counter mode) before reading the SID registers. So if the GCLK signal is lost, it can also be detected by the negate-bit toggle function.

#### 8.3.4.7 LOD LSD Self-Test

The HT1388 device implements an LOD\_LSD self-test function to check the LOD\_LSD detection circuit to improve the system reliability. If the LOD\_LSD detection circuit fails to detect the LED failure, the LOD\_LSD self-test Function can identify and report the malfunction.

The LOD\_LSD self-test function can be executed by sending the LOD\_LSD self-test command. LOD\_LSD\_FLAG is 000b by default. After the LOD\_LSD self-test command, if there is no fault on LOD\_LSD detection circuit, and the LOD\_LSD\_FLAG value is 011b. If there are failures on the LOD\_LSD detection circuits, the LOD\_LSD\_FLAG value is 110b, the ERRn pin is pulled low, and the bit values stay unchanged until the fault is removed and an ERROR clear command is executed. If the LOD\_LSD\_FLAG is neither 011b nor 110b, there should be something wrong in the self-test procedure.

#### 8.3.4.8 ERRn Pin

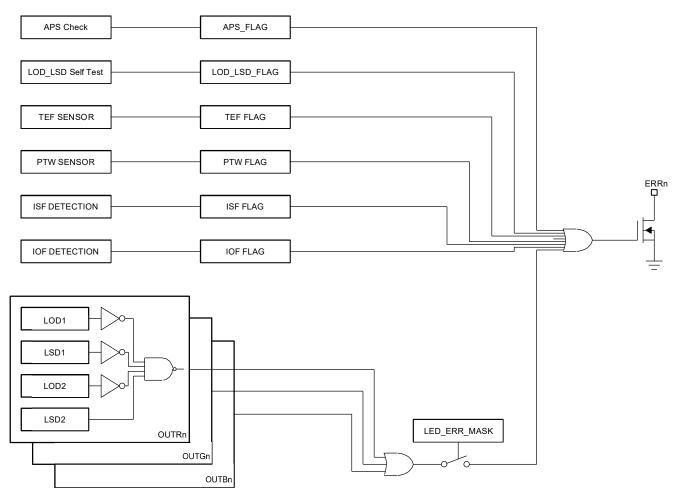

The HT1388 device supports an active-low open-drain error output. Figure 24 shows the error pulldown block diagram. 10-bit error status information controls the error pulldown circuit directly. But LED failure can be masked by the LED\_ERR\_MASK bit. The LED\_ERR\_MASK value is 1 by default, so an LED failure is masked from the error pulldown circuit. Even if there is an LED failure, the ERRn pin is not pulled down by this LED failure. If LED\_ERR\_MASK is 0, the ERRn pin is pulled down by an LED failure to indicate an error scenario. Users can use an MCU interrupt to read out the fault information.

11/2021 ver.1 Private & Confidential 20

Figure 24. ERRn Pin Pulldown Scheme

#### 8.3.4.9 ERROR Clear

This command is used to clear the error flags in the error status register and APS register. The A53h 12-bit command code indicates an ERROR clear command. After executing the ERROR clear command, the 132-bit LOD\_LSD registers, 1-bit NEG1, 1-bit NEG2, 10-bit error status and 33-bit adjacent-pin-short results are loaded into the common shift register. The error status registers and APS registers are reset to 0 if the error is removed. See Figure 9 for more detail.

#### 8.3.4.10 Global Reset

This command is used to implement a power-on reset with software input. The A5Ch 12-bit command code initiates a global reset command. After executing the global reset command, all internal registers are reset to their default values. See Figure 10 for more detail.

#### 8.3.4.11 Slew Rate Control

To improve system EMI performance, the HT1388 device implements a programmable slew rate control for the output channels. This output slew rate is configured by the SLEW\_RATE bit in the FC-BC-DC register. The SLEW\_RATE bit is 0 by default, and the rising and falling time of the output is 200 ns. When the SLEW\_RATE bit is 1, the rising and falling time of each output is 100 ns.

#### 8.3.4.12 Channel Group Delay

Large surge currents may flow through the system if all 33 channels turn on simultaneously. These large current surge could induce detrimental noise and electromagnetic interference (EMI) into other circuits. The HT1388 device implements channel turn-on delay for each group to reduce the surge current. The output current sinks are grouped into six groups.

```

Group 1: OUTR0, -G0, -B0, OUTR6, -G6, -B6.

Group 2: OUTR1, -G1, -B1, OUTR7, -G7, -B7.

Group 3: OUTR2, -G2, -B2, OUTR8, -G8, -B8.

Group 4: OUTR3, -G3, -B3, OUTR9, -G9, -B9.

Group 5: OUTR4, -G4, -B4, OUTR10, -G10, -B10.

Group 6: OUTR5, -G5, -B5,

```

Group 6. OO 1 No, -Go, -Bo,

All group 2 channels turn on and off 50 ns later then group 1 channels, all group 3 channels turn on and off later than group 2 channels, all group 4 channels turn on and off 50 ns later than group 3 channels, all group 5 channels turn on and off 50 ns later than group 4 channels, and all group 6 channels turn on and off 50 ns later than group 5 channels. Figure 1 shows the details.

#### 8.4 Device Functional Modes

#### 8.4.1 Power Up

To make the device work normally, users must provide two power supplies to the HT1388 device. One is  $V_{CC}$ , 3 V–5.5 V, for device internal logic power. The other is a supply up to 5V, which is the power supply for the LED loads. To make sure the LED diagnostics feature works normally, the LED supply must connect to the SENSE pin directly.

#### 8.4.2 Device Initialization

After device power on, users must send the error clear command and global reset command to initialize the device and make sure there are no existing faults on the circuit.

#### 8.4.3 Fault Mode

The HT1388 has full diagnostics features. The device can detect faults and latch the faults into registers. For device faults such IREF resistor open or short, the device enters a self-protection scenario. The device reports the faults and sets the output current to a default value. For the overtemperature fault, the device turns off the output channels and latches the fault into the TEF register. Except for these two faults, for all other faults including LED faults, the device only detects and report the faults, but does not take actions to handle the faults, and the channels keep their configured status. Users must read out the faults and decide how to handle the faults.

#### 8.4.4 Normal Operation

Users must program the device through the serial interface for normal operation. Users write to the FC-BC-DC registers to set the operation mode and output current, write to the grayscale registers to set the PWM duty cycle for each channel, and read the SID registers to get device fault information.

#### 8.5 Programming

#### 8.5.1 Register Write and Read

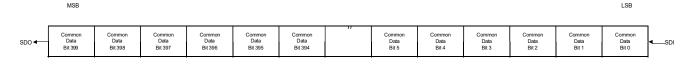

The HT1388 device is programmable via serial interface. It contains a 400-bit common shift register to shift data from SDI into the device. The register LSB connects to SDI and the MSB connects to SDO. On each SCK rising edge, the data on SDI shifts into the register LSB and all 400 data bits shift towards the MSB. The data appears on SDO when the 400-bit common shift register overflows.

The HT1388 data write command contains 400-bit data, the first 4 MSB bits from bit 399 to bit 396 are reserved and ignored. According to the following different criteria, there are three types of data write commands: FC-BC-DC write, GS data write, and special command.

- When LATCH is high at the 400th SCK rising edge, and when the 12 bits from bit 395 to bit 384 of the 400-bit data are 0, the 268 LSBs of 400-bit data shift to the function control (FC), brightness control (BC) and dot correction (DC) registers on the LATCH rising edge, as shown in Figure 2.

- When LATCH is low at the 400th SCK rising edge, the 396 LSBs of 400-bit data shifts into the grayscale (GS) configuration registers on the LATCH rising edge, as shown in Figure 1.

- When LATCH is high at the 400th SCK rising edge, and when the 12 bits from bit 395 to bit 384 of the 400-bit data match any of the twelve 12-bit command codes, the device executes the corresponding command after the LATCH rising edge, as shown in Special Command Function.

When the device powers on, the default value of the 400-bit common shift register is 0.

Figure 25. HT1388 Common Register

#### 8.5.1.1 FC-BC-DC Write

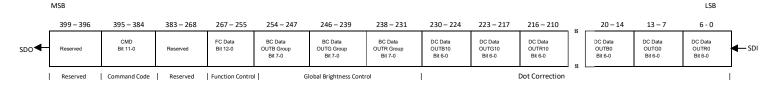

The device latches the 268 LSBs of data in the 400-bit common shift register into the FC-BC-DC registers at the rising edge of the latch signal when the 12 bits from bit 395 to bit 384 of the 400-bit data are 0.

When the device is powered on, the FC-BC-DC data latch is reset to all 0s except for the LED\_ERR\_MASK bit which is 1. Therefore, data must be written to the 400-bit common shift register and latched into the FC-BC-DC registers before turning on the constant-current outputs. It is better to keep BLANK low to prevent the outputs from turning on.

Figure 26. FC-BC-DC Register

11/2021 ver.1 Private & Confidential 23

#### 8.5.1.1.1 FC Data Write

The FC data is 13 bits in length, located from bit 267 to bit 255. See Table 12 for the detailed description. The default value for all FC data is 0, except for the LED\_ERR\_MASK bit which is 1.

**Table 12. Function-Control Data-Bit Assignment**

| BIT     | NAME         | DESCRIPTION                                                                                                                                                                             |

|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 267     | LED_ERR_MASK | LOD-LSD failure or PWM error information mask bit 0b = Any LOD-LSD failure or PWM error pulls down the ERRn pin 1b = LOD-LSD failure or PWM error is masked from affecting the ERRn pin |

| 266     | SLEW_RATE    | Turnon and turnoff speed configuration bit 0b = 200 ns rising and falling time. 1b = 100 ns rising and falling time.                                                                    |

| 265     | LOD_VOLATGE  | LED open-detection (LOD) threshold 0b = LOD threshold is 0.3 V 1b = LOD threshold is 0.5 V                                                                                              |

| 264     | LSD_VOLTAGE  | LED short-detection (LSD) threshold $0b = LSD$ threshold is $V_{SENSE} - 0.3$ V $1b = LSD$ threshold is $V_{SENSE} - 0.7$ V                                                             |

| 265     | APS_CURRENT  | Adjacent-pin short-detection sink current 0b = 20-µA APS current 1b = 40-µA APS current                                                                                                 |

| 262     | APS_TIME     | Adjacent-pin short-detection time 0b = 10 µs APS detection time 1b = 20 µs APS detection time                                                                                           |

| 261–260 | GS_MODE      | Grayscale-counter mode selection. 00/01b = 12-bit mode 10 = 10-bit mode 11 = 8-bit mode                                                                                                 |

| 259     | TIMING_RESET | Display-timing reset mode 0b = Disabled 1b = Enabled                                                                                                                                    |

| 258     | AUTO_REPEAT  | Auto-display repeat mode 0b = Disabled 1b = Enabled                                                                                                                                     |

| 257     | DC_RANGE_B   | Dot-correction adjustment range for the BLUE color output 0b = Lower range 0%–66.7%                                                                                                     |

| 256     | DC_RANGE_G   | 1b = Higher range  Dot-correction adjustment range for the GREEN color output  0b = Lower range 0%–66.7%  1b = Higher range                                                             |

| 255     | DC_RANGE_R   | Dot–correction adjustment range for the RED color output  0b = Lower range 0%–66.7%  1b = Higher range                                                                                  |

The grayscale counter has 12-bit, 10-bit and 8-bit configurations. Bits 261–260 in the FC register configure the grayscale counter mode.

**Table 13. GS Counter Mode Table**

| GRAYSCALE COUNTE | FUNCTION MODE |                                                                         |

|------------------|---------------|-------------------------------------------------------------------------|

| BIT 261          | BIT 260       | FUNCTION MODE                                                           |

| 0                | Don't care    | 12-bit counter mode                                                     |

| 1                | 0             | 10-bit counter mode, the lowest 10 bits of the 12-bit GS data are valid |

| 1                | 1             | 8-bit counter mode, the lowest 8 bits of the 12-bit GS data are valid   |

#### 8.5.1.1.2 BC Data Write

The BC data is 24 bits length which locates from bit 254 to bit 231. The data of the BC data latch are used to adjust the constant-current values for eleven channel constant-current drivers of each color group. The current can be adjusted from 0% to 100% of each output current adjusted by brightness control with 8-bit resolution.

Table 14. Brightness Control Data Bit Assignments

| BITS    | BRIGHTNESS CONTROL DATA |

|---------|-------------------------|

| 254–247 | OUTB0-OUTB7 group       |

| 246–239 | OUTG0-OUTG7 group       |

| 238–231 | OUTR0-OUTR7 group       |

#### 8.5.1.1.3 DC Data Write

The DC data is 231 bits in length, located from bit 230 to bit 0. The HT1388 device can adjust the output current of each channel using the DC function. The DC function has two adjustment ranges with 7-bit resolution. Table 15 shows the DC data assignments in the DC registers. The high adjustment range DC can adjust output current from 33.3% to 100% of  $I_{(OUT)max}$ . The low adjustment range DC can adjust output current from 0% to 66.7% of  $I_{(OUT)max}$ . The range control is in bits 257–255 in the function control data latch select the high or low adjustment. Bit 257 controls the OUTB DC range. Bit 256 controls the OUTG DC range, Bit 255 controls the OUTR DC range. For details, see Table 12

**Table 15. DC Data Assignments**

| BITS    | DATA   | BITS    | DATA  |

|---------|--------|---------|-------|

|         |        | 118–112 | OUTG5 |

| 230-224 | OUTB10 | 111–105 | OUTR5 |

| 223-217 | OUTG10 | 104–98  | OUTB4 |

| 216-210 | OUTR10 | 97–91   | OUTG4 |

| 209-203 | OUTB9  | 90–84   | OUTR4 |

| 202-196 | OUTG9  | 83–77   | OUTB3 |

| 195-189 | OUTR9  | 76–70   | OUTG3 |

| 188-182 | OUTB8  | 69–63   | OUTR3 |

| 181-175 | OUTG8  | 62–56   | OUTB2 |

## Table 15. DC Data Assignments (continued)

| BITS    | DATA  | BITS  | DATA  |

|---------|-------|-------|-------|

| 174-168 | OUTR8 | 55–49 | OUTG2 |

| 167–161 | OUTB7 | 48–42 | OUTR2 |

| 160–154 | OUTG7 | 41–35 | OUTB1 |

| 153–147 | OUTR7 | 34–28 | OUTG1 |

| 146–140 | OUTB6 | 27–21 | OUTR1 |

| 139–133 | OUTG6 | 20–14 | OUTB0 |

| 132–126 | OUTR6 | 13–7  | OUTG0 |

| 125–119 | OUTB5 | 6–0   | OUTR0 |

## Table 16. Output Current vs DC (High DC Range)

|                  |                  |                  |                  | ` •                  | • .                                           |                                          |

|------------------|------------------|------------------|------------------|----------------------|-----------------------------------------------|------------------------------------------|

| DC DATA<br>(BIN) | DC DATA<br>(DEC) | DC DATA<br>(HEX) | BC DATA<br>(HEX) | CURRENT<br>RATIO (%) | CURRENT<br>(I <sub>(OUT)max</sub> = 30<br>mA) | CURRENT<br>(I <sub>(OUT)max</sub> = 2 mA |

| 000 0000         | 0                | 00               | FF               | 33.3                 | 10.00                                         | 0.67                                     |

| 000 0001         | 1                | 01               | FF               | 33.9                 | 10.16                                         | 0.68                                     |

| 000 0010         | 2                | 02               | FF               | 34.4                 | 10.31                                         | 0.69                                     |

|                  |                  | •••              |                  |                      |                                               |                                          |

| 111 1101         | 125              | 7D               | FF               | 99                   | 29.69                                         | 1.98                                     |

| 111 1110         | 126              | 7E               | FF               | 99.5                 | 29.84                                         | 1.99                                     |

| 111 1111         | 127              | 7F               | FF               | 100                  | 30.00                                         | 2                                        |

## Table 17. Output Current vs DC (Low DC Range)

| DC DATA<br>(BIN) | DC DATA<br>(DEC) | DC DATA<br>(HEX) | BC DATA<br>(HEX) | CURRENT<br>RATIO (%) | CURRENT<br>(I <sub>(OUT)max</sub> = 30<br>mA) | CURRENT<br>(I <sub>(OUT)max</sub> = 2 mA |

|------------------|------------------|------------------|------------------|----------------------|-----------------------------------------------|------------------------------------------|

| 000 0000         | 0                | 00               | FF               | 0                    | 0.00                                          | 0                                        |

| 000 0001         | 1                | 01               | FF               | 0.5                  | 0.16                                          | 0.01                                     |

| 000 0010         | 2                | 02               | FF               | 1.0                  | 0.31                                          | 0.02                                     |

|                  |                  |                  |                  |                      |                                               |                                          |

| 111 1101         | 125              | 7D               | FF               | 65.6                 | 19.69                                         | 1.31                                     |

| 111 1110         | 126              | 7E               | FF               | 66.1                 | 19.84                                         | 1.32                                     |

| 111 1111         | 127              | 7F               | FF               | 66.7                 | 20.00                                         | 1.33                                     |

### Table 18. Output Current vs BC (High DC Range)

|                  |                  |                  |                  | ` ` `                | J - /                                         |                                               |

|------------------|------------------|------------------|------------------|----------------------|-----------------------------------------------|-----------------------------------------------|

| BC DATA<br>(BIN) | BC DATA<br>(DEC) | BC DATA<br>(HEX) | DC DATA<br>(HEX) | CURRENT<br>RATIO (%) | CURRENT<br>(I <sub>(OUT)max</sub> = 30<br>mA) | CURRENT<br>(I <sub>(OUT)max</sub> = 2 mA<br>) |

| 0000 0000        | 0                | 00               | 7F               | 0                    | 0.00                                          | 0                                             |

| 0000 0001        | 1                | 01               | 7F               | 0.4                  | 0.12                                          | 0.01                                          |

| 0000 0010        | 2                | 02               | 7F               | 0.8                  | 0.24                                          | 0.02                                          |

|                  | •••              | •••              |                  |                      |                                               |                                               |

| 1111 1101        | 253              | FD               | 7F               | 99.2                 | 29.76                                         | 1.98                                          |

| 1111 1110        | 254              | FE               | 7F               | 99.6                 | 29.88                                         | 1.99                                          |

| 1111 1111        | 255              | FF               | 7F               | 100                  | 30.00                                         | 2                                             |

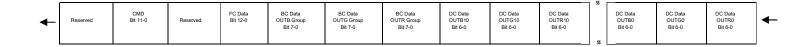

#### 8.5.1.2 Grayscale Data Write

The grayscale data, which is 396 bits long, contains a 12-bit grayscale value for each output. The grayscale value sets the channel turn-on time. Figure 27 shows the GS register configuration. Figure 1 is the GS write timing diagram. The 396 LSBs Data is latched from the 400-Bit common shift register into the GS data latch at the rising edge of the LATCH pin. When data is latched into the GS registers, the new data is immediately available on the constant- current outputs. If data are latched with BLANK high, the outputs may turn on or off unexpectedly. So users should update the GS data when BLANK is low.

The 12-bit GS function has 4096 brightness steps, from 0% to 99.97% brightness. The GS function is controlled by a 12-bit GS counter. The GS counter increments on each rising edge of the grayscale reference clock, GCLK. The falling edge of BLANK resets the GS counter value to 0. The GS counter value stays 0 while BLANK is low, even if there is a GCLK input. Pulling BLANK high enables the 12-bit GS counter. The first rising edge of a GS clock after BLANK goes high increments the GS counter by 1 and turns on the outputs. Each additional rising edge increases the GS counter by 1. The GS counter monitors the number of clock pulses on the GCLK pin. The output stays on while the counter value is less than or equal to the GS setting value. The output turns off at the rising edge of the GS counter value when the counter is higher than the GS setting value. Table 20 is the on-time duty cycle of each GS data bit when 12-bit GS counter mode selected.

When the device is powered up, the 400-bit common shift register and GS data latch are reset to 0.

Equation 4 describes each output on time.

$$t_{on} = t_{GCLK} \times GS$$

where

- $\bullet \quad \ \ t_{GCLK} \ \text{is the GS clock period} \\$

- GS is the programmed grayscale value for each output

(4)

Equation 5 shows the duty cycle calculation equation.

$$Dutycycle = \frac{GS}{4096}$$

(5)

Figure 27. HT1388 Grayscale Register

Once the GS data is latched into the GS registers at the rising edge of the LATCH signal, the FC-BC-DC data latch shifts into the lowest 268 bits of the common shift register. So, the FC-BC-DC data can be read out from SDO in GS write. This FC-BC-DC read function can also be realized by the read FC-BC-DC command, see FC-BC-DC Read for the timing diagram.

Table 19. Grayscale Data Bit Assignments

| · · · · · · · · · · · · · · · · · · · |        |  |  |

|---------------------------------------|--------|--|--|

| BITS                                  | DATA   |  |  |

| 395-384                               | OUTB10 |  |  |

| 383-372                               | OUTG10 |  |  |

| 371-360                               | OUTR10 |  |  |

| 359-348                               | OUTB9  |  |  |

| 347-336                               | OUTG9  |  |  |

11/2021 ver.1 **Private & Confidential** 27

| 335-324 | OUTR9 |

|---------|-------|

| 323-312 | OUTB8 |

| 311-300 | OUTG8 |

| 299-288 | OUTR8 |

| 287-276 | OUTB7 |

| 275-264 | OUTG7 |

| 263-252 | OUTR7 |

| 251-240 | OUTB6 |

| 239-228 | OUTG6 |

| 227-216 | OUTR6 |

| 215-204 | OUTB5 |

| 203-192 | OUTG5 |

| 191-180 | OUTR5 |

| 179-168 | OUTB4 |

| 167-156 | OUTG4 |

| 155-144 | OUTR4 |

| 143-132 | OUTB3 |

| 131-120 | OUTG3 |

| 119-108 | OUTR3 |

| 107-96  | OUTB2 |

| 95-84   | OUTG2 |

| 83-72   | OUTR2 |

| 71-60   | OUTB1 |

| 59-48   | OUTG1 |

| 47-36   | OUTR1 |

| 35-24   | OUTB0 |

| 23-12   | OUTG0 |

| 11-0    | OUTR0 |

|         |       |

Table 19. Grayscale Data Bit Assignments (continued)

Table 20. GS Data vs Output On Time

| GS DATA (BINARY) | GS DATA (DECIMAL) | GS DATA (HEX) | DUTY CYCLE (%) | ON-TIME BASED ON 33-<br>MHz GS CLOCK (ns) |

|------------------|-------------------|---------------|----------------|-------------------------------------------|

| 0000 0000 0000   | 0                 | 000           | 0              | 0                                         |

| 0000 0000 0001   | 1                 | 001           | 0.02           | 30                                        |

| 0000 0000 0010   | 2                 | 002           | 0.05           | 61                                        |

|                  |                   |               |                |                                           |

| 0111 1111 1111   | 2047              | 7FF           | 49.97          | 62 030                                    |

| 1000 0000 0000   | 2048              | 800           | 50.00          | 62 061                                    |

| 1000 0000 0001   | 2049              | 801           | 50.02          | 62 091                                    |

|                  |                   |               |                |                                           |

| 1111 1111 1101   | 4093              | FFD           | 99.93          | 124 030                                   |

| 1111 1111 1110   | 4094              | FFE           | 99.95          | 124 061                                   |

| 1111 1111 1111   | 4095              | FFF           | 99.98          | 124 091                                   |

## 7.5.1.3 Special Command Function

There are twelve special command codes defined in the HT1388 device, shown in Table 21. To input the command, the level of LATCH at the last SCK before the LATCH rising edge must be high, and the highest 12 bits should be one of the listed 12 command codes. In this condition, the device ignores other bits and no data are latched into FC-BC-DC registers. Normally users can write other bits to 0 in the special command. The corresponding command function executes after the rising edge of the LATCH signal.

If no special command code is identified, the command is a NULL command and no special command is executed. The command is the same as the FC-BC-DC write function.

**Table 21. Special Command Codes**

| COMMAND           | COMMAND CODE           | FUNCTION                                                                                                                                                                                                                                                                          |

|-------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lookahead         | A5Dh (1010 0101 1101b) | Sets lookahead pin value to 1, to preview the target trimming value                                                                                                                                                                                                               |

| Zap               | A5Eh (1010 0101 1110b) | Sends a ZAP pulse action to burn out the fuse                                                                                                                                                                                                                                     |

| Sleep             | A58h (1010 0101 1000b) | Enters Sleep mode. When sleep mode is entered, all analog peripherals will be turn off while the value set at the FC-BC-DC and GS Data registers would be retained.                                                                                                               |

| Wakeup            | A5Ah (1010 0101 1010b) | Exits Sleep mode. When exiting sleep mode, the logic will gate the signals to the analog block until the analog_rdy signal is high.                                                                                                                                               |

| GS read           | 5AFh (0101 1010 1111b) | Load GS data into common register.                                                                                                                                                                                                                                                |

| SID read          | 5A3h (0101 1010 0011b) | Load SID data into common register.                                                                                                                                                                                                                                               |

| FC-BC-DC read     | 5ACh (0101 1010 1100b) | Load FC-BC-DC data into common register. This reading function can also be achieved by GS data write.                                                                                                                                                                             |

| APS check         | 53Ah (0101 0011 1010b) | Adjacent pin short detection, APS test starts at the rising edge of Latch signal, then set APS register(24bits) and APS_Flag in SID register according to the test result. Keep all channels off during this test.                                                                |

| LOD_LSD self-test | 535h (0101 0011 0101b) | LOD-LSD detector circuit self test and set LOD_LSD_FLAG in SID register according to the test result.                                                                                                                                                                             |

| Negate bit toggle | 55Ah (0101 0101 1010b) | Toggle Negate Bit. When Negate Bit = 0, the 48 bits LOD-LSD detector output data will be latched into LOD1-LSD1 and LOD2-LSD2 register without invert. When Negate Bit =1, the 48 bits LOD-LSD detector output data will invert, and latch into LOD1-LSD1 and LOD2-LSD2 register. |

| ERROR clear  | A53h (1010 0101 0011b)                   | Load SID data into common register, and then reset the Error status register and APS register to 0. |

|--------------|------------------------------------------|-----------------------------------------------------------------------------------------------------|

| GLOBAL reset | A5Ch (1010 0101 1100b)                   | All internal registers are reset. The command has the same function as power on reset.              |

| NULL         | Different from any of the above commands | The same function as FC-BC-DC write.                                                                |

#### 8.5.1.3.1 GS Read

The GS read command loads 396-bits of GS data into the lowest 396 bits of the common shift register. By applying 400 SCK clocks, the GS data shifts out from the SDO pin. For details, see Figure 3.

#### 8.5.1.3.2 FC-BC-DC Read

There are two ways to read the FC-BC-DC data latch.

One way is latching data into the GS data latch. After the GS write finishes, the FC-BC-DC data latches into the lowest 268 bits of the common shift register.

Another way is using the FC-BC-DC read command. After the FC-BC-DC read command finishes, the FC-BC-DC data latches into the lowest 268 bits of the common shift register.

By applying 400 SCK clocks, the FC-BC-DC data shifts out from the SDO pin. For details, see Figure 8.

#### 8.5.1.3.3 Status Information Data Read